On March 14th, Elon Musk posted a single line on X.

“Terafab Project launches in 7 days.”

I work as a semiconductor engineer in Silicon Valley. My network is full of engineers from NVIDIA, Broadcom, AMD, Qualcomm, SK Hynix, and basically every major chip company you can name. When I brought up Terafab, the reaction was unanimous.

“Lol.”

Terafab. Bigger than a gigafactory, hence “tera.” Logic, memory, and packaging all under one roof. Hundreds of billions of chips per year. And apparently he wants to smoke cigars and eat cheeseburgers inside the fab while doing it.

Terafab is bullshit.

At least that’s what a regular semiconductor engineer like me thinks.

But then again, Elon has always been that guy.

The one who solves problems that the experts in those fields said were unsolvable.

Rockets. Electric cars. Satellite internet. Every single time.

And yet, part of me can’t stop wondering how Elon is going to pull this off anyway.

This article covers two things. First, why running a semiconductor fab is so brutally hard, from the perspective of someone who has worked on the foundry side. Why the cigar comment made the industry laugh. What 2nm actually means. Why yield is not a problem you can throw money at.

Second, what Terafab might actually look like in practice. The moves already happening at Samsung Taylor. The Intel rumors. The packaging line in Texas where equipment is already being moved in.

This is Terafab story, seen through the eyes of an ordinary engineer.

What’s confirmed and what’s vision

First, let’s separate known facts from Elon’s vision. Mixing them together clouds the judgment.

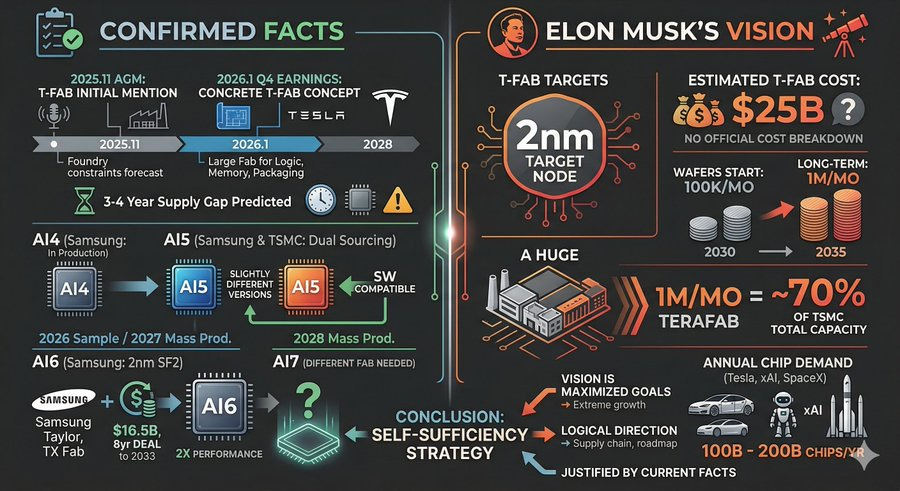

The confirmed facts: Elon first publicly mentioned Terafab at the annual shareholder meeting in November 2025, saying something to the effect of “even the best-case projections from foundries fall short of what we need.” The idea got more concrete during the Q4 2025 earnings call on January 28, 2026. Elon said Tesla needs to build “a very large fab in the US that includes logic, memory, and packaging,” and warned that chip supply constraints would hit within three to four years.

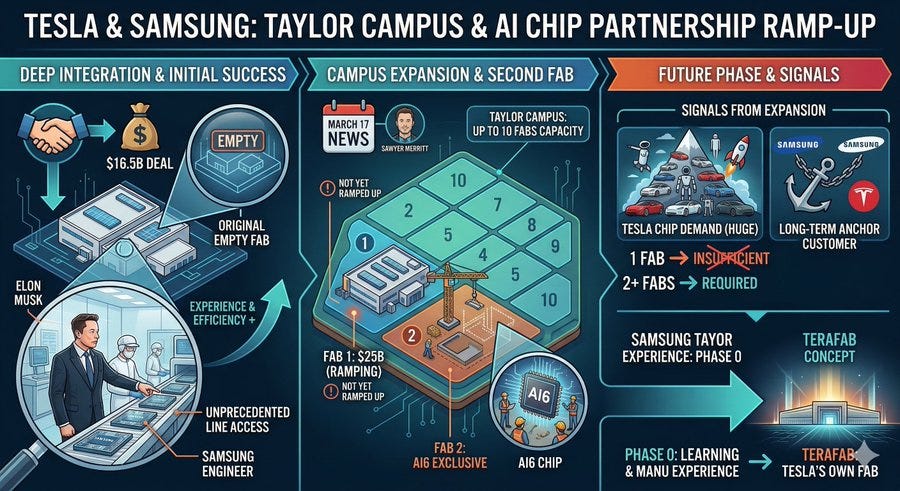

Tesla’s current chip manufacturing lineup is also confirmed. AI4 is made by Samsung. AI5 runs at both TSMC and Samsung in “slightly different versions” because the two foundries have fundamentally different process characteristics, so the software is designed to run on both. Samples in 2026, mass production in 2027. AI6 goes on Samsung’s 2nm SF2 process, locked in through a $16.5B long-term deal signed in July 2025 at Samsung’s Taylor, Texas fab, running through 2033. AI6 targets roughly 2x the performance of AI5, with mass production around mid-2028.

And Elon has said directly that AI7 onward would need “a different fab” or “something more adventurous.” The general read in the industry is that this refers to Terafab.

From here it shifts into Elon’s vision and press-based speculation. The target process node is reportedly 2nm, with a projected cost around $25B, though Tesla has never published detailed cost figures. The ramp from 100,000 wafer starts per month to eventually 1 million is based on Elon’s own statements. One million wafers a month, by the way, is roughly 70% of TSMC’s entire current monthly output. From a single facility. The figure of 100 to 200 billion chips per year comes from Elon’s own estimates of combined demand across Tesla, xAI, and SpaceX.

The “vision” part is Elon doing what Elon does: setting maximum targets. You don’t have to take it at face value. But the direction itself, that Tesla needs to control its own chip supply, is logically sound based on the confirmed facts alone.

“We’ll smoke cigars in the cleanroom”: what this one line reveals

If you want to compress the semiconductor industry’s reaction to Terafab into a single moment, it’s the cleanroom comment.

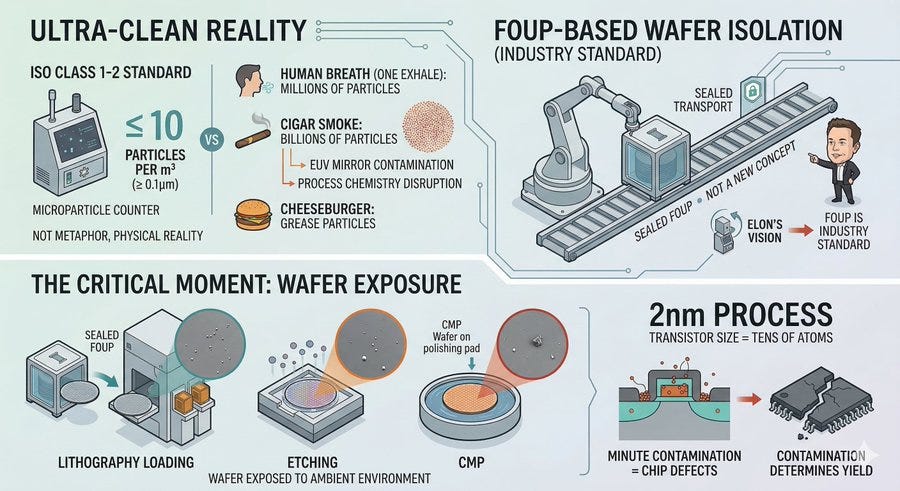

In a January 2026 interview on the Moonshots podcast, Elon said: “I think the latest fabs are building cleanrooms wrong. I’ll make a bet. If Tesla builds a 2nm fab, we’ll be able to eat cheeseburgers and smoke cigars inside it.”

His logic: if you keep the wafers sealed inside nitrogen-purged containers throughout the entire process, you don’t need to maintain the surrounding environment at ISO Class 1 levels. Wafer isolation is the key, not building-wide cleanliness.

Why did this get laughed at?

Modern advanced fabs run at ISO Class 1 to 2. That means fewer than 10 particles larger than 0.1 micrometers per cubic meter. One human breath releases millions of particles. A cigar? Billions of particles, plus organic contaminants that degrade EUV mirror surfaces and corrupt process chemistry. The grease from a cheeseburger works the same way. This is not metaphor. It is physics.

The FOUP-based wafer isolation Elon is describing is already standard practice. Wafers travel in sealed FOUPs inside fabs. That’s not new. The problem is that wafers have to leave the FOUP. When loading into lithography tools. When entering etching, deposition, CMP chambers. At those moments, the wafer is exposed to the surrounding environment. That exposure window is what determines yield.

TSMC spends billions on cleanrooms for a reason. It’s not ignorance or tradition. It’s because they’ve spent decades correlating environmental contamination data against defect density at the atomic level. At 2nm, a single transistor is tens of atoms across. One contamination event kills the whole chip.

Jensen Huang publicly warned Elon not to underestimate the difficulty. “Advanced semiconductor manufacturing is extremely hard. It’s not just building a factory. The engineering, the science, and the artistry of what TSMC does are extremely difficult.” To reporters, he went further, saying catching up to TSMC is “virtually impossible.”

The cleanroom comment matters not just because it’s technically wrong. It suggests Elon either doesn’t fully understand the complexity of semiconductor manufacturing yet, or is deliberately oversimplifying to sell the vision. Both are problems. The first means he’ll hit reality hard during execution. The second means he’s setting unrealistic expectations for investors.

Why Terafab doesn’t make sense, from someone who’s been inside a foundry

The cleanroom is just the beginning.

I’ve done post-silicon debug and yield improvement work at Samsung Foundry, Qualcomm, and AMD. I’ve seen how chips get made from both inside and outside the foundry. From that vantage point, Terafab has more than one or two realistic barriers.

1. The physical reality of building a fab

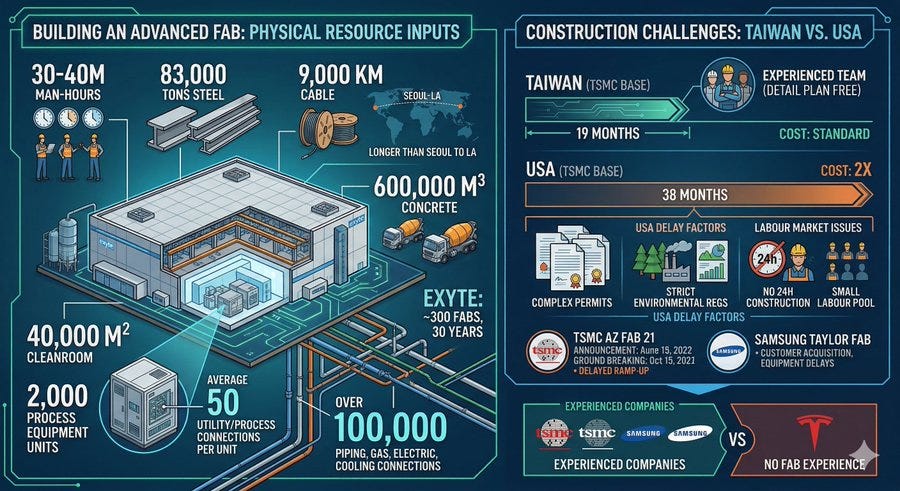

Building an advanced fab is not constructing a building. Exyte, a firm that has built roughly 300 fabs over 30 years, says a large advanced fab requires 30 to 40 million man-hours. 83,000 tons of steel. 9,000 kilometers of cable (longer than the distance from Seoul to Los Angeles). 600,000 cubic meters of concrete. Inside the building, you’re looking at about 40,000 square meters of cleanroom, 2,000 process tools, each one averaging 50 individual utility and process connections. That’s more than 100,000 pipe, gas, electrical, and coolant connections that all have to work together inside one facility.

In Taiwan, building a fab at this scale takes about 19 months. In the US? 38 months. Twice as long. Roughly twice the cost. And that’s using a company that has built fabs for decades. The US is slower because the permitting process is complex, environmental regulations are strict, 24-hour construction is hard to sustain given labor rules, and the pool of workers with fab construction experience is thin. Exyte’s CTO Herbert Blaschitz said Taiwan’s construction workforce is so experienced with fab builds that they can work without detailed drawings. That depth doesn’t exist in the US.

TSMC Arizona Fab 21 is the real-world data point. Announced in 2020, broke ground in 2021, original 2024 production target slipped due to workforce and supply chain problems. Samsung Taylor had its own delays from lack of customers and equipment delivery issues. These are the outcomes from companies that have been building fabs for decades. Tesla has never built one.

2. The technical complexity of 2nm

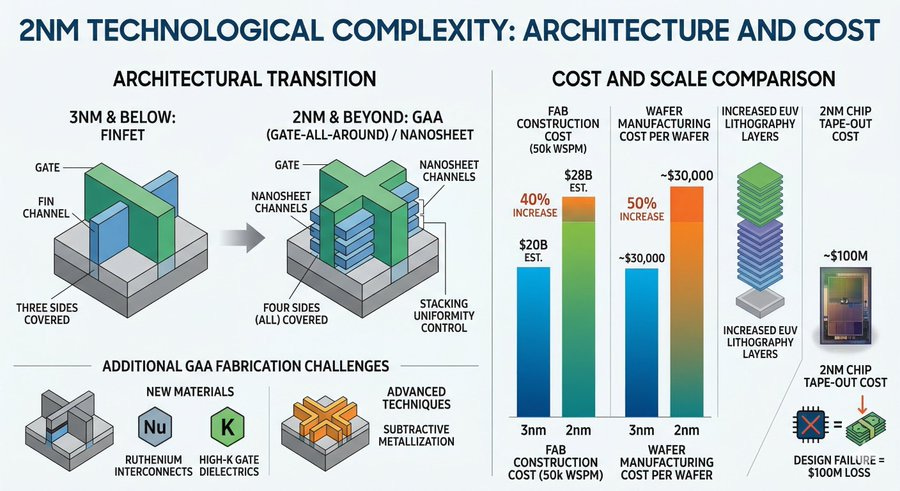

“2nm” is not just drawing smaller circuits. The transistor architecture itself changes.

FinFET, the 3D transistor structure the industry has used for years, hits its limits at 3nm. At 2nm you have to switch to Gate-All-Around, specifically nanosheet structures. FinFET wraps the gate around three sides of the channel. GAA wraps all four. This is the biggest architectural shift since the transition from planar to FinFET. You can reuse a lot of process modules, but nanosheet stacking uniformity control, new materials like ruthenium interconnects and high-k gate dielectrics, and techniques like subtractive metallization all have to be figured out from scratch.

The numbers: IBS estimates a 2nm fab at 50,000 wafer starts per month costs about $28B to build. That’s roughly 40% more than a 3nm fab at $20B. A 2nm wafer costs around $30,000 each to manufacture, about 50% more than 3nm. A large portion of that increase comes from the additional EUV lithography layers. Tape-out costs at 2nm run about $100M. One bad design decision, $100M gone.

3. Yield: the most brutal part

This is the real issue.

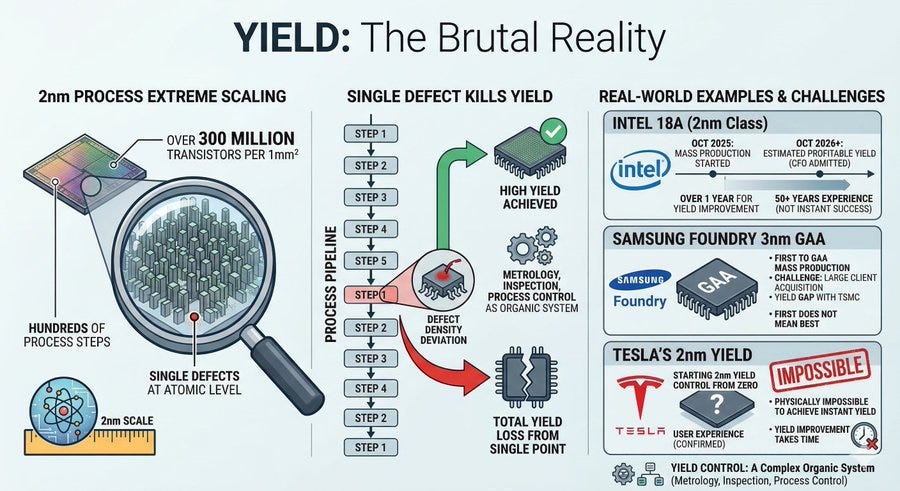

At 2nm, you’re fitting more than 300 million transistors into one square millimeter. A wafer goes through hundreds of process steps. If defect density drifts out of spec at any single step, yield collapses. Controlling this requires metrology, inspection, and process control working as one integrated system.

Intel 18A is the relevant case study. Volume production started in October 2025. Intel’s own CFO admitted that reaching “profitable yield levels” won’t happen until late 2026. A company with over 50 years of experience takes more than a year to get yield under control on a new node. Samsung Foundry’s 3nm GAA process is a more painful example. They were first to market with GAA in volume production, but the yield gap versus TSMC has made it extremely hard to win large customers. Being first did not mean being good.

Tesla starting at 2nm and nailing yield from the beginning? Having worked in yield improvement, I’d say that’s close to impossible.

4. Equipment: the bottleneck money can’t fix

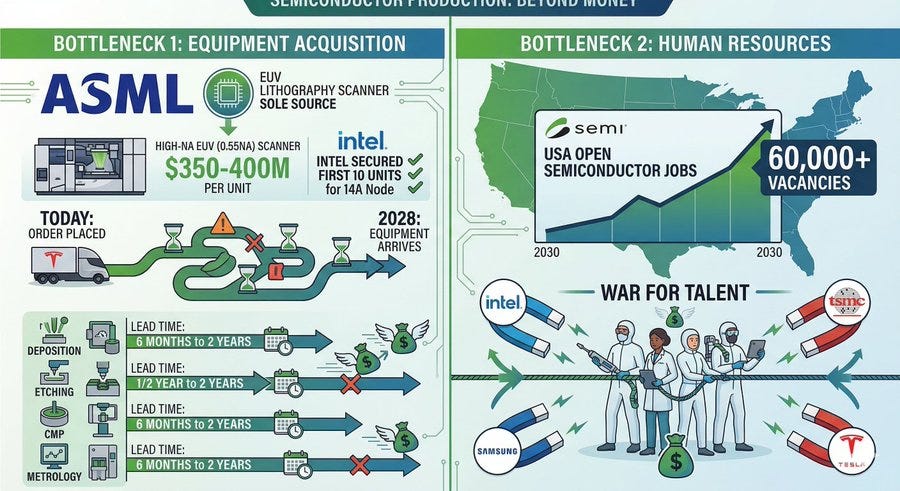

EUV lithography scanners are made by one company on earth: ASML. The next-generation High-NA EUV at 0.55NA runs $350 to $400 million per unit. Intel has already locked up the first ten units of High-NA EUV production for its 14A node. If Tesla placed an order today, the tools wouldn’t arrive until 2028 at the earliest. Beyond EUV, a fab needs hundreds of other tool types across deposition, etching, CMP, and metrology, each with lead times ranging from six months to two years.

The workforce problem mirrors the equipment problem. SEMI projects that more than 60,000 semiconductor jobs in the US alone will go unfilled through 2030. With Intel, TSMC, and Samsung all building US fabs at the same time, adding Tesla to that competition would make the talent shortage significantly worse.

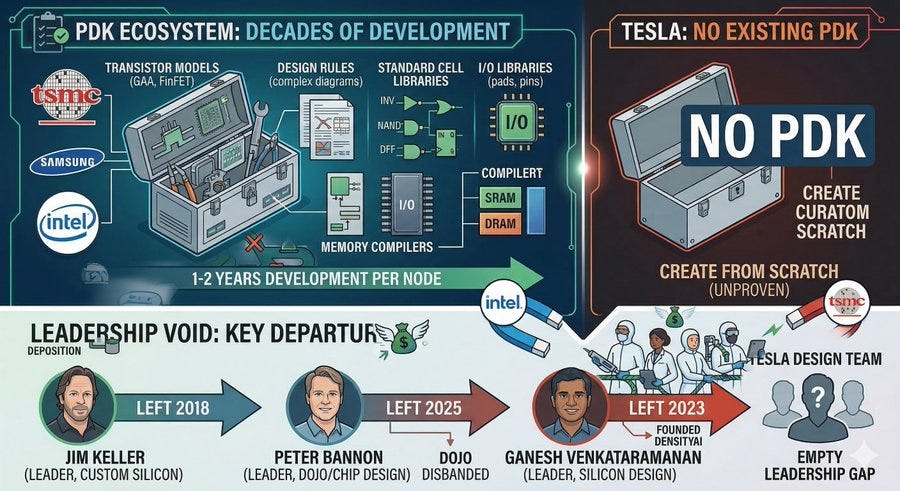

5. No design ecosystem: there’s no PDK

Building a fab is not enough to make chips. You need a PDK, a Process Design Kit. That means transistor models, design rules, standard cell libraries, I/O libraries, memory compilers, all of it. TSMC, Samsung, and Intel have developed their PDKs over decades. Developing a PDK for a new node and getting it certified with EDA tools takes one to two years on its own. If Tesla runs its own fab, it has to build the PDK from zero.

Does Tesla have the people to do that? Jim Keller left in 2018. Peter Bannon exited in 2025 when Dojo was wound down. Ganesh Venkataramanan left in 2023 to found DensityAI. There are meaningful gaps in Tesla’s custom silicon leadership right now.

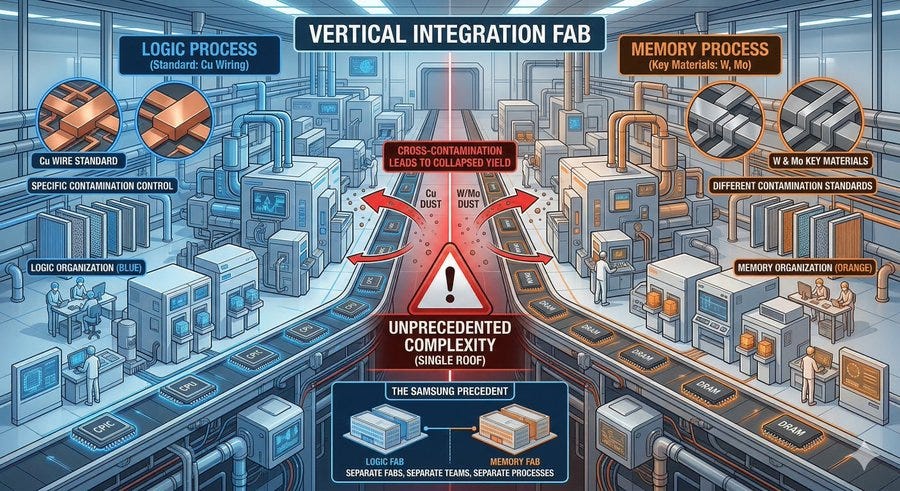

6. Logic and memory together? The complexity of vertical integration

Logic and memory processes are fundamentally different. Different materials, different equipment, different contamination control standards. Logic fabs use copper for metal interconnects. DRAM relies on tungsten and molybdenum. Cross-contamination between those materials in a shared cleanroom destroys yield. Samsung does both logic and memory, but in separate fabs, run by separate organizations, on separate processes. Combining them under one roof is a completely different problem.

Why you can’t dismiss Elon outright

That’s the ordinary engineer’s read on Terafab.

But as I said at the start, Elon has heard this kind of skepticism his entire career. The important thing is that the industry’s “that won’t work” verdict has been wrong repeatedly.

SpaceX. In 2002, a guy with no aerospace background said he was going to build rockets. The first three Falcon 1 launches failed. When the company had enough money left for exactly one more attempt, the fourth launch succeeded. Elon himself said he gave it a 10% chance of success. Today SpaceX is the world’s largest commercial launch provider, launching rockets every few days.

Tesla nearly went bankrupt in 2008. Model 3 production became “production hell.” Bankruptcy rumors circulated every quarter. He pushed through anyway.

Gigafactory. Starlink. Both were dominated by skepticism at the start. And in every case, what got him through was a specific problem-solving framework he applies obsessively.

Elon’s five-step algorithm, applied to Terafab

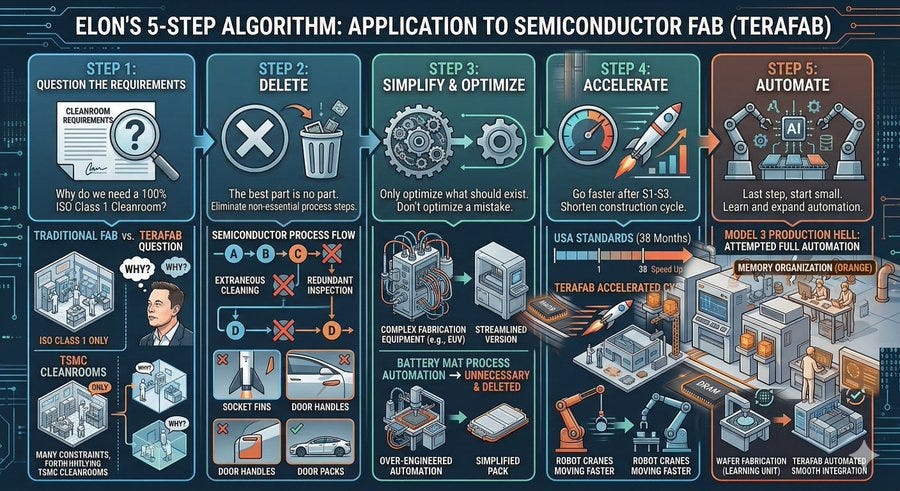

Elon uses what Walter Isaacson called “The Algorithm” in his biography, a five-step problem-solving framework he applies across SpaceX and Tesla manufacturing. Here’s how it maps onto Terafab.

Step 1: Question every requirement. “Why does the entire cleanroom need to be ISO Class 1?” The cigar comment is technically oversimplified, but asking “why?” about something TSMC has taken for granted for 37 years is exactly this step.

Step 2: Delete. “The best part is no part.” Semiconductor process steps are so interdependent that there’s far less room to delete than in rocket manufacturing. But in the fab construction process itself, there’s likely plenty of inefficiency that can be stripped out.

Step 3: Simplify and optimize. “The most common mistake of smart engineers is optimizing something that shouldn’t exist.” Tesla famously spent huge effort automating a battery mat step in Model 3 production before realizing the mat itself was unnecessary.

Step 4: Accelerate. “If you’re digging your own grave, don’t dig faster.” Speed only comes after steps one through three. Cutting the US fab construction cycle from 38 months is where this applies.

Step 5: Automate. “The big mistake in my factories was trying to automate every step from the beginning.” The lesson from Model 3 production hell. Terafab won’t be a fully automated 2nm facility from day one. The realistic path is small scale, learn, then expand.

Can these five steps be applied to the semiconductor process itself? Honestly, I’m still pretty skeptical. But I think they can be applied to fab construction and fab operations. Not the process chemistry, but the infrastructure, logistics, and construction methodology around it. There are almost certainly inefficiencies that the fab industry treats as standard practice, and that’s probably where Elon starts.

What it actually looks like in practice

The most important question isn’t “will Terafab happen or not.” It’s “if it happens, what form does it take.”

Samsung Taylor: the zeroth step

The real significance of the $16.5B deal is not the contract size. It’s that Elon reportedly wants to go inside Samsung’s production lines and work directly on improving efficiency. That kind of access is not available to a typical fabless customer. It was only possible because Samsung’s Taylor fab was sitting largely empty without committed customers.

There’s also news from today, March 17th. Samsung is preparing to build a second fab dedicated to AI6 at the Taylor campus. The first $25B fab hasn’t even ramped yet, and they’re already starting a second one. That signals Tesla’s chip demand will outstrip a single fab’s capacity. The Taylor campus can reportedly accommodate up to ten fabs.

My read: the experience Tesla accumulates at Samsung Taylor, the process engineering knowledge, the yield improvement methodology, the equipment operating expertise, that’s the zeroth step of Terafab.

Packaging: the most certain first move

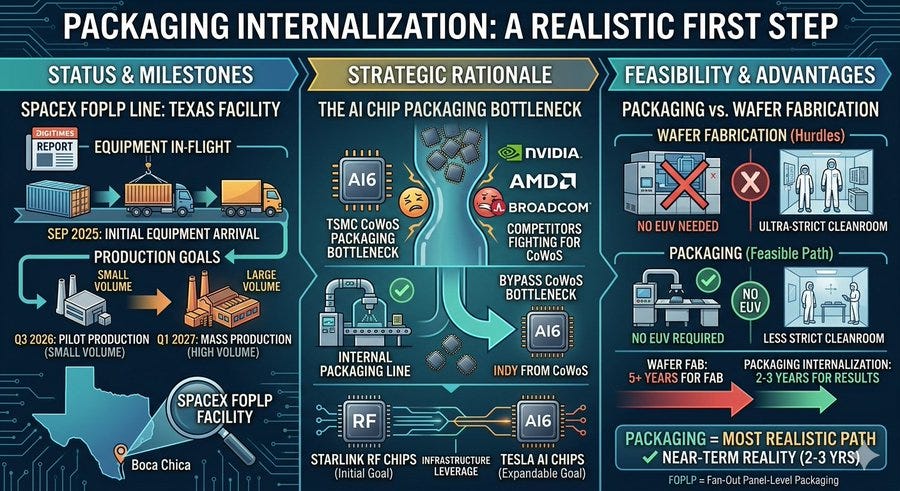

According to DigiTimes, SpaceX’s FOPLP (Fan-Out Panel-Level Packaging) line in Texas started receiving equipment in September 2025. Target is low-volume production in Q3 2026, with full production in Q1 2027. It starts with RF chip packaging for Starlink satellites, but that same infrastructure can be directly extended to Tesla AI chip packaging.

Why does packaging matter. The biggest physical bottleneck in the AI chip market right now is TSMC’s CoWoS packaging capacity. NVIDIA, AMD, and Broadcom are all fighting over CoWoS allocation. If Tesla controls its own packaging line, it escapes that bottleneck entirely. Packaging also has a much lower barrier to entry than wafer fabrication. No EUV required. Cleanroom standards are less demanding. This is the most realistic path to meaningful results within two to three years.

Intel: the door is open

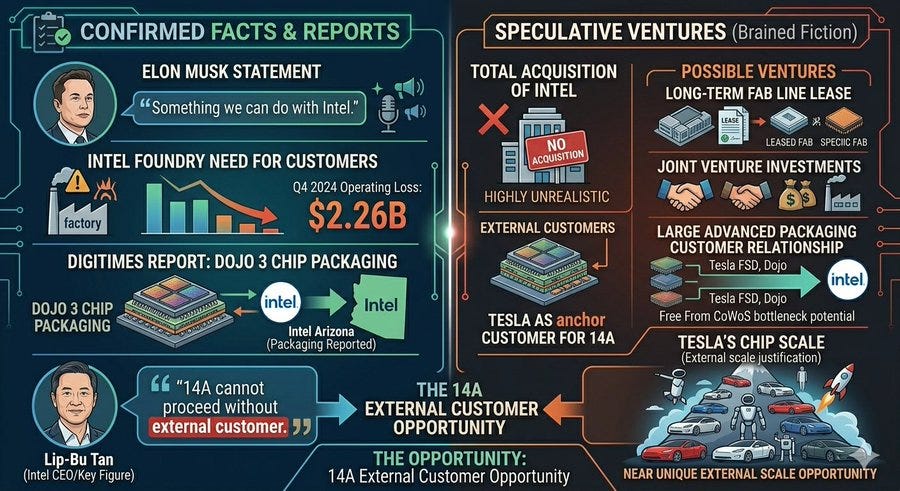

Sticking to confirmed facts: Elon has publicly said he thinks there’s something to do with Intel. Intel Foundry desperately needs external customers (operating loss of $2.26B in Q4 2024). DigiTimes has reported that Dojo 3 chip packaging may be handled at Intel’s Arizona facility. If that’s accurate, a working relationship already exists.

From here it’s speculation. A full Tesla acquisition of Intel is not realistic. But a long-term lease of specific Intel Foundry fab lines, a JV-style co-investment, or a large advanced packaging customer relationship is all plausible. Intel CEO Lip-Bu Tan has admitted directly that “14A cannot move forward without external customers.” Tesla is one of the very few companies with the volume to make that argument credible.

The Battery Day lesson: the real goal is leverage

At Battery Day in 2020, Elon announced in-house production of 4680 cells. The target of 100 GWh by 2022 was badly missed. But eventually it worked, and in the process Tesla built negotiating leverage over Panasonic and CATL. It was not full independence, but the existence of the option, “we can make these ourselves,” changed the negotiating dynamic completely.

Terafab is likely the same pattern. The end goal is not “100% self-manufactured chips.” It’s “we will not be held hostage by chip supply.” The announcement of building a fab is itself a negotiating card against TSMC and Samsung. That works even before the fab ever turns on.

Between bullshit and vision

I’m a working semiconductor engineer. I’ve been through Samsung, Qualcomm, and AMD. I’ve seen chips designed, manufactured, tested, and ramped into production. I have enough experience in this field to speak with some credibility about how hard semiconductor manufacturing actually is.

So when I look at Terafab as stated, I think there’s a large gap between the vision and reality. The cigar comment, taken at face value, sounds like someone who hasn’t fully internalized what semiconductor manufacturing involves.

At the same time, I think Tesla’s semiconductor insourcing will move forward in some form. There is clear internal demand at serious scale (FSD, Cybercab, Optimus, xAI). Manufacturing partner diversification is already underway. The foundry learning that’s starting at Samsung Taylor is real. The FOPLP line in Texas is physically in motion. And above all, there’s Elon’s consistent track record and The Algorithm.

It makes sense that Terafab looks like bullshit to a lot of people.

SpaceX did too. So did Tesla. So did Starlink.

I believe Elon can make it

Another enjoyable read. Thank you. Musk's comments about Intel are interesting.